锁相环路是一种反馈电路,锁相环的英文全称是Phase-Locked Loop,简称PLL。其作用是使得电路上的时钟和某一外部时钟的相位差同步。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

在数据采集系统中,锁相环是一种非常有用的同步技术,因为通过锁相环,可以使得不同的数据采集板卡共享同一个采样时钟。因此,所有板卡上各自的本地 80MHz和20MHz时基的相位都是同步的,从而采样时钟也是同步的。因为每块板卡的采样时钟都是同步的,所以都能严格地在同一时刻进行数据采集。锁相环路是一个相位反馈自动控制系统。它由以下三个基本部件组成:鉴相器(PD)、环路滤波器(LPF)和压控振荡器(VCO)。

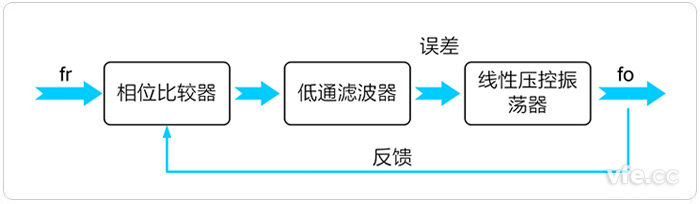

图1是基本锁相环电路的框图。PLL是由相位比较器(也称鉴相器)、低通滤波器(LPF)和线性压控振荡器(VCO)三部分组成。

图1 锁相环电路构成原理框图

相位比较器将来自压控振荡的输出频率fo与外加参考频率fr做比较,产生一个与相位差对应的误差电压输出至低通滤波器。

低通滤波器将相位检波器的输出滤波后,转换成平滑的直流控制电压,是锁相环电路的重要组成部分。由于滤波器有一定的时间常数,所以PLL的锁定不是瞬时的,因而VCO的输出频率锁定在参考电压fo的平均值上,而不是锁定在瞬时值,这一特性利于将带噪声的输入参考频率形成纯净的输出频率。

误差电压经LPF滤波后馈入VCO的控制输入端,这样就可使fo和fr之间减少相位差逐步恒定,这时,环路就称为被锁定了,即锁定状态。

如果VCO的频率在开始时低于输入参考频率,响应比较器的输出偏正,此正输出电压经滤波后加至VCO,强制VCO的频率增加,直至VCO的频率和相应输入参考信号的频率相同为止;如果VCO的频率增加到高于输入参考频率,则发生与上述相反的过程,相应比较器的输出减少,使VCO的频率降低,以锁定到与输入参考相同的频率上。

锁相环技术的应用比较广泛,主要包括:倍频、频率合成、FM解调器、音频解码等。

例如利用锁相环路的频率跟踪特性,可实现分频、倍频、混频等频谱变换功能,并从而构成频率综合器与标准频率源。

上一篇:直驱永磁式风力发电机

下一篇:电子负载